Strasser Florian Johann BSc.

# Profiling of Real-Time Operating System Services for Singlecore and Multicore Processors

# MASTER'S THESIS

to achieve the university degree of Diplom-Ingenieur Master's degree programme: Telematics

submitted to

# Graz University of Technology

Assessor: Dipl.-Ing. Dr. techn. Kreiner Christian Supervisor: BSc. Dipl.-Ing. Höller Andrea

Institute of Technical Informatics

Graz, December 2014

## Abstract

When designing a real-time system, early key decisions include the selection of the processor and real-time operating system (RTOS). During the comparison of the design options, performance characteristics are one of the most important features that should be considered. Additionally, in order to perform a scheduling analysis, it is necessary to be aware of the RTOS overhead. Nowadays, there is a trend to use multicore processors in hard real-time systems. However, how can we measure the runtimes of an RTOS on a multicore processor? It is common practice for companies to profile the RTOS for every platform and configuration. This is known to be an error prone task, because there is no company independent profiling suite for RTOS services. In this master thesis, an extendable and portable profiling suite including the most common RTOS profiling procedures for singlecore and multicore processors is proposed. The profiling suite contains singlecore RTOS metrics defined in Rhealstone. Furthermore, these profiling procedures are adopted to be compatible with multicore processors. For the implementation the singlecore platform i.MX28 and the multicore platform i.MX6Q are chosen and the QNX Neutrino RTOS and SafeRTOS are used.

### Kurzfassung

Wenn man ein Echtzeitsystem entwickelt stellen sich am Anfang zwei Schlüsselfragen. Welcher Prozessor und welches Echtzeitbetriebssystem soll verwendet werden? Eine der wichtigsten Attribute bei der Auswahl ist die Performance des Echtzeitbetriebssystem. Die Performance des Echtzeitbetriebssystem ist auch ein wichtiger Faktor wenn man die Schedulability eines harten Echtzeitsystems berechnet. Es ist zu beobachten, dass bei der Entwicklung von eingebetteten Echtzeitsystemen immer häufiger Mehrkernprozessoren eingesetzt werden. Daher stellt sich die Frage, wie man die Laufzeiten von Echtzeitbetriebssystemen auf solchen komplexen Ein- und Mehrkernsystemen messen soll. Es ist gängige Praxis das Echtzeitbetriebssystem direkt auf der verwendeten Hardware auszumessen. Das ist allerdings ein sehr fehleranfälliger Prozess, da es dafür keine einheitliche und unabhängige Toolbox gibt. In der vorliegenden Arbeit geht es um die Entwicklung einer erweiterbaren und portablen Toolbox für die Profilierung von Echtzeitbetriebssystemen. Diese Toolbox enthält die gängigsten Profilierungs-Prozeduren für die am häufigsten verwendeten Echtzeitbetriebssystem Services wie sie in Rhealstone vorgeschlagen werden. Diese Echtzeitbetriebssystem Metriken wurden erweitert um auch Mehrkernsysteme zu unterstützen. Für die Implementierung wurden die Freescale Prozessoren i.MX287 und i.MX6Q und die Echtzeitbetriebssysteme SafeRTOS und QNX Neutrino verwendet.

# EIDESSTATTLICHE ERKLÄRUNG

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt, und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe. Das auf TUGRAZonline hochgeladene Dokument ist identisch mit der hier vorliegende Arbeit.

Graz,am .....

(Unterschrift)

# AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present master's thesis dissertation.

date

(signature)

## Danksagung

Diese Diplomarbeit wurde im (Studien)Jahr 2014 am Institut für Technische Informatik an der Technischen Universität Graz durchgeführt.

Hiermit möchte ich mich beim Institut für Technische Informatik (ITI) und den Professoren für die Betreuung und Unterstützung bedanken. Mein spezieller Dank gilt Andrea Höller und Christian Kreiner. Dank ihrer qualifizierten und engagierten Betreuung konnte dieses Projekt im geplanten Zeitraum durchgeführt werden. Zudem konnte dank den Mitarbeitern des ITI die für diese Arbeit benötigte Hard- und Software schnell und unkompliziert Organisiert werden. Weiters danke ich dem Brandschutzbeauftragtem für die sofortige Entfernung der illegalen Couch aus unserem Büro. Durch den Wegfall meines Mittagsschläfchens auf selbiger Couch konnte meine Produktivität gesteigert werden. Neben den Mitarbeitern des Instituts möchte ich mich auch bei all meinen Freunden

für das Verständnis während dieser schweren Zeit danken. Dank ihrer nur allzu häufigen Unterstützung als lebendige Debug Duck<sup>1</sup> konnte ich zahlreiche Fehler finden und vermeiden. Ein besonderes Dankeschön möchte ich hier meiner Familie und meiner Mutter, Helga Nagler, aussprechen. Ihre tatkräftige Unterstützung machte es erst möglich, dass ich mein Studium so problemlos abschließen konnte.

Graz, im Jänner 2015

Strasser Florian

<sup>&</sup>lt;sup>1</sup>http://en.wikipedia.org/wiki/Rubber\_duck\_debugging Online accessed 19.01.2015

# Contents

| 1        | Intr | roduction                                             | 11        |

|----------|------|-------------------------------------------------------|-----------|

|          | 1.1  | Motivation                                            | 11        |

|          | 1.2  | Goals                                                 | 13        |

|          | 1.3  | Outline                                               | 13        |

| <b>2</b> | Tec  | hnical Background and Related Work                    | <b>14</b> |

|          | 2.1  | Real-time Systems                                     | 14        |

|          | 2.2  | Real-time Operating Systems                           | 14        |

|          |      | 2.2.1 Processes and Tasks                             | 15        |

|          |      | 2.2.2 Scheduling                                      | 15        |

|          |      | 2.2.3 Interprocess Communication                      | 16        |

|          |      | 2.2.4 Interrupts                                      | 16        |

|          |      | 2.2.5 Priority Inversion                              | 16        |

|          |      | 2.2.6 Application Programming Interface               | 16        |

|          | 2.3  | Timing Analysis                                       | 17        |

|          |      | 2.3.1 Static Timing Analysis                          | 17        |

|          |      | 2.3.2 Dynamic Timing Analysis                         | 18        |

|          |      | 2.3.3 Simulation                                      | 19        |

|          | 2.4  | Measurement of Real-time Operating System Performance | 19        |

|          |      | 2.4.1 Benchmarking and Profiling                      | 19        |

|          |      | 2.4.2 Metrics of an Real-time Operating System        | 19        |

|          |      | 2.4.3 Benchmarking Methods                            | 23        |

|          |      | 2.4.4 Measurement                                     | 24        |

|          |      | 2.4.5 Results and Interpretation                      | 24        |

|          | 2.5  | Hardware Architecture of Real-time Systems            | 25        |

|          |      | 2.5.1 Cache                                           | 25        |

|          |      | 2.5.2 Singlecore Platforms and i.MX28                 | 26        |

|          |      | 2.5.3 Introduction to Multicore Platforms             | 26        |

|          |      | 2.5.4 Memory Architecture of Multicore Platforms      | 26        |

|          | 2.6  | Real-time Operating Systems for Multicore Platforms   | 28        |

|          |      | 2.6.1 Operating Modes                                 | 28        |

|          |      | 2.6.2 Thread Safety                                   | 29        |

|          |      | 2.6.3 Debugging on a Multicore Platform               | 29        |

|          |      | 2.6.4 Available RTOS Implementations                  | 30        |

|          | 2.7  | Related Work                                          | 30        |

|   |     | 2.7.1          | Timing Analysis on Small Scale RTOS                         | 80         |

|---|-----|----------------|-------------------------------------------------------------|------------|

|   |     | 2.7.2          |                                                             | 31         |

|   |     | 2.7.3          | -                                                           | 32         |

|   |     | 2.7.4          |                                                             | 33         |

| _ | ~   |                |                                                             |            |

| 3 |     | -              | 0                                                           | 55         |

|   | 3.1 | -              |                                                             | 35         |

|   | 3.2 |                |                                                             | 86         |

|   |     | 3.2.1          | 0                                                           | 86         |

|   |     | 3.2.2          | ũ là chí                | 86         |

|   |     | 3.2.3          | 1 0 0                                                       | 87         |

|   | 3.3 |                |                                                             | 87         |

|   |     | 3.3.1          | 1 5                                                         | 87         |

|   |     | 3.3.2          | 1                                                           | 39         |

|   |     | 3.3.3          | 0                                                           | 39         |

|   |     | 3.3.4          |                                                             | 10         |

|   |     | 3.3.5          | 0                                                           | 1          |

|   |     | 3.3.6          |                                                             | 11         |

|   | 3.4 | Select         | ion and Adaption of Profiling Procedures for RTOS Metrics 4 | 1          |

|   |     | 3.4.1          | Realization of Measurements with Cache Related              |            |

|   |     |                | r · · · · · · · · · · · · · · · · · · ·                     | 12         |

|   |     | 3.4.2          | Context Switch Time                                         | 12         |

|   |     | 3.4.3          | Preemption Time 4                                           | 13         |

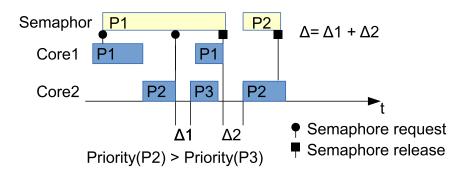

|   |     | 3.4.4          | Semaphore Shuffle Time 4                                    | 14         |

|   |     | 3.4.5          | Deadlock Break Time                                         | 15         |

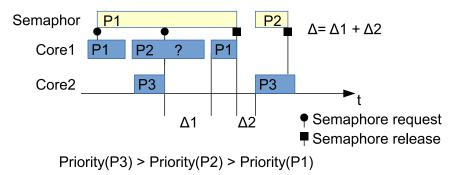

|   |     | 3.4.6          | Intertask Message Latency                                   | <b>!</b> 7 |

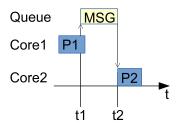

|   | 3.5 | Profili        | ng Suite for RTOS Metrics 4                                 | 18         |

|   |     | 3.5.1          | Overview                                                    | 18         |

|   |     | 3.5.2          | Profiling Procedures for RTOS Metrics                       | 19         |

|   |     | 3.5.3          | Measurement                                                 | <b>1</b> 9 |

|   |     | 3.5.4          |                                                             | 51         |

|   |     | 3.5.5          | Extendability                                               | 52         |

|   |     | 3.5.6          | Logging and Output 5                                        | 52         |

|   |     | 3.5.7          |                                                             | 53         |

| 4 | Imr | olemen         | tation 5                                                    | 54         |

| 4 | 4.1 |                |                                                             | 54         |

|   | 7.1 | 4.1.1          |                                                             | 54         |

|   |     | 4.1.2          |                                                             | 56         |

|   |     | 4.1.3          |                                                             | 56         |

|   | 4.2 |                |                                                             | 56         |

|   | 4.2 | 4.2.1          | 0                                                           | 50<br>57   |

|   |     | 4.2.1<br>4.2.2 | 1                                                           | 57         |

|   |     | 4.2.2<br>4.2.3 |                                                             |            |

|   |     | 4.2.3<br>4.2.4 | 0                                                           | 57<br>.0   |

|   |     |                | 8                                                           | 58<br>. 0  |

|   |     | 4.2.5          | Finalizing and Clean Up                                     | 68         |

| 4.2.7       Message Passing         4.3       Abstractions         4.3.1       RTOS Abstraction         4.3.3       Evaluation of Measurement Techniques         4.4       QNX Neutrino on i.MX6Q         4.4.1       Development Environment         4.4.2       Bord Support Package Configuration         4.4.3       Performance Monitoring Unit         4.4.4       Timer         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.5       SafeRTOS on i.MX287         4.5.1       Development Platform         4.5.2       Timer         4.5.3       MyBarrier         4.5.4       Task Configuration         4.5.5       CRPD Simulation         5.1       SafeRTOS on i.MX28         5.1.1       Statistics         5.1.2       Precision         5.1.3       Figures         5.1.4       Discussion         5.2       QNX Neutrino in Singlecore mode on i.MX6Q         5.2.1       Statistics         5.2.2       Precision         5.3.3       Figures         5.3.4       Discussion         5.3.2       Precision         5.3.3 <th>6<br/>7</th> <th></th>                                 | 6<br>7   |                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------|

| 4.2.7       Message Passing         4.3       Abstractions         4.3.1       RTOS Abstraction         4.3.2       Hardware Abstraction         4.3.3       Evaluation of Measurement Techniques         4.4       QNX Neutrino on i.MX6Q         4.4.1       Development Environment         4.4.2       Bord Support Package Configuration         4.4.3       Performance Monitoring Unit         4.4.4       Timer         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.5.2       Timer         4.5.3       MyBarrier         4.5.4       Task Configuration         4.5.5       CRPD Simulation         4.5.6       Task Configuration         4.5.7       Timer         4.5.8       Task Configuration         4.5.9       CRPD Simulation         5.1       SafeRTOS on i.MX28         5.1.1       Statistics         5.1.2       Precision         5.1.3       Figures         5.1.4       Discussion         5.2       QNX Neutrino in Singlecore mode on i.MX6Q                                               | O        |                                                                                                            |

| 4.2.7       Message Passing         4.3       Abstractions         4.3.1       RTOS Abstraction         4.3.2       Hardware Abstraction         4.3.3       Evaluation of Measurement Techniques         4.4       QNX Neutrino on i.MX6Q         4.4.1       Development Environment .         4.4.2       Bord Support Package Configuration         4.4.3       Performance Monitoring Unit         4.4.4       Timer         4.4.5       Task Configuration         4.4.5       Task Configuration         4.4.5       Task Configuration         4.4.5       Task Configuration         4.5       SafeRTOS on i.MX287         4.5.1       Development Platform         4.5.2       Timer         4.5.3       MyBarrier         4.5.4       Task Configuration         4.5.5       CRPD Simulation         5.1       SafeRTOS on i.MX28         5.1.1       Statistics         5.1.2       Precision         5.1.3       Figures         5.1.4       Discussion         5.2       QNX Neutrino in Singlecore mode on i.MX6Q         5.2.1       Statistics         5.2.2       Precision                                       | c        | Conclusion                                                                                                 |

| 4.2.7       Message Passing         4.3       Abstractions         4.3.1       RTOS Abstraction         4.3.2       Hardware Abstraction         4.3.3       Evaluation of Measurement Techniques         4.4       QNX Neutrino on i.MX6Q         4.4.1       Development Environment         4.4.2       Bord Support Package Configuration         4.4.3       Performance Monitoring Unit         4.4.4       Timer         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.5       SafeRTOS on i.MX287         4.5.1       Development Platform         4.5.2       Timer         4.5.3       MyBarrier         4.5.4       Task Configuration         4.5.5       CRPD Simulation         4.5.5       CRPD Simulation         5.1       SafeRTOS on i.MX28         5.1.1       Statistics         5.1.2       Precision         5.1.3       Figures         5.1.4       Discussion         5.2       QNX Neutrino in Singlecore mode on i.MX6Q         5.2.1       Statistics                                         |          |                                                                                                            |

| 4.2.7       Message Passing         4.3       Abstractions         4.3.1       RTOS Abstraction         4.3.2       Hardware Abstraction         4.3.3       Evaluation of Measurement Techniques         4.4       QNX Neutrino on i.MX6Q         4.4.1       Development Environment         4.4.2       Bord Support Package Configuration         4.4.3       Performance Monitoring Unit         4.4.4       Timer         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.5       SafeRTOS on i.MX287         4.5.1       Development Platform         4.5.2       Timer         4.5.3       MyBarrier         4.5.4       Task Configuration         4.5.5       CRPD Simulation         4.5.6       Task Configuration         4.5.7       Task Configuration         4.5.8       Sill SafeRTOS on i.MX28         5.1.1       Statistics         5.1.2       Precision         5.1.3       Figures         5.1.4       Discussion         5.2       QNX Neutrino in Singlecore mode o                               |          |                                                                                                            |

| 4.2.7       Message Passing         4.3       Abstractions         4.3.1       RTOS Abstraction         4.3.2       Hardware Abstraction         4.3.3       Evaluation of Measurement Techniques         4.4       QNX Neutrino on i.MX6Q         4.4.1       Development Environment         4.4.2       Bord Support Package Configuration         4.4.3       Performance Monitoring Unit         4.4.4       Timer         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.4.6       CRPD Simulation         4.4.6       CRPD Simulation         4.5.1       Development Platform         4.5.2       Timer         4.5.3       MyBarrier         4.5.4       Task Configuration         4.5.5       CRPD Simulation         4.5.6       CRPD Simulation         4.5.7       Timer         4.5.8       MyBarrier         4.5.9       CRPD Simulation         5       Results         5.1.1       StafeRTOS on i.MX28         5.1.1       StafeRTOS on i.MX28         5.1.2       Precision         5.1.3       Figures         5.1.4                                                              |          | 0                                                                                                          |

| 4.2.7       Message Passing         4.3       Abstractions         4.3.1       RTOS Abstraction         4.3.2       Hardware Abstraction         4.3.3       Evaluation of Measurement Techniques         4.4       QNX Neutrino on i.MX6Q         4.4.1       Development Environment         4.4.2       Bord Support Package Configuration         4.4.3       Performance Monitoring Unit         4.4.4       Timer         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.4.6       CRPD Simulation         4.5       SafeRTOS on i.MX287         4.5.1       Development Platform         4.5.2       Timer         4.5.3       MyBarrier         4.5.4       Task Configuration         4.5.5       CRPD Simulation         4.5.6       CRPD Simulation         5.1       SafeRTOS on i.MX28         5.1.1       Stafestics         5.1.2       Precision         5.1.3       Figures         5.1.4       Discussion         5.2       QNX Neutrino in Singlecore mode on i.MX6Q         5.2.1       Statistics         5.2.2       Precision                                                  |          |                                                                                                            |

| 4.2.7       Message Passing .         4.3       Abstractions .         4.3.1       RTOS Abstraction         4.3.2       Hardware Abstraction .         4.3.3       Evaluation of Measurement Techniques         4.4       QNX Neutrino on i.MX6Q .         4.4.1       Development Environment .         4.4.2       Bord Support Package Configuration .         4.4.3       Performance Monitoring Unit .         4.4.4       Timer .         4.4.5       Task Configuration .         4.4.6       CRPD Simulation .         4.4.5       Task Configuration .         4.4.6       CRPD Simulation .         4.5.1       Development Platform .         4.5.2       Timer .         4.5.3       MyBarrier .         4.5.4       Task Configuration .         4.5.5       CRPD Simulation .         4.5.4       Task Configuration .         4.5.5       CRPD Simulation .         5.1       SafeRTOS on i.MX28 .         5.1.1       Statistics .         5.1.2       Precision .         5.1.3       Figures .         5.1.4       Discussion .         5.2.2       Precision .         5.2.3 <td< td=""><td></td><td></td></td<> |          |                                                                                                            |

| 4.2.7       Message Passing .         4.3       Abstractions .         4.3.1       RTOS Abstraction         4.3.2       Hardware Abstraction         4.3.3       Evaluation of Measurement Techniques         4.4       QNX Neutrino on i.MX6Q         4.4       QNX Neutrino on i.MX6Q         4.4.1       Development Environment         4.4.2       Bord Support Package Configuration         4.4.3       Performance Monitoring Unit         4.4.4       Timer         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.4.5       SafeRTOS on i.MX287         4.5.1       Development Platform         4.5.2       Timer         4.5.3       MyBarrier         4.5.4       Task Configuration         4.5.5       CRPD Simulation         4.5.6       CRPD Simulation         4.5.7       Timer         4.5.8       MyBarrier         4.5.9       CRPD Simulation         5.1       SafeRTOS on i.MX28         5.1.1       Statistics         5.1.2       Precision         5.1.3       Figures         5.1.4       Discussion         5.                                                         |          | • •                                                                                                        |

| 4.2.7       Message Passing         4.3       Abstractions         4.3.1       RTOS Abstraction         4.3.2       Hardware Abstraction         4.3.3       Evaluation of Measurement Techniques         4.4       QNX Neutrino on i.MX6Q         4.4       QNX Neutrino on i.MX6Q         4.4.1       Development Environment         4.4.2       Bord Support Package Configuration         4.4.3       Performance Monitoring Unit         4.4.4       Timer         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.5.1       Development Platform         4.5.2       Timer         4.5.3       MyBarrier         4.5.4       Task Configuration         4.5.5       CRPD Simulation         4.5.6       CRPD Simulation         5.1       SafeRTOS on i.MX28         5.1.1       Statistics         5.1.2       Precision         5.1.3       Figures         5.1.4       Discussion         5.2       QNX Neutrino in Singlecore mode on i.MX6Q         5.2.3       Figures                                         |          |                                                                                                            |

| 4.2.7       Message Passing         4.3       Abstractions         4.3.1       RTOS Abstraction         4.3.2       Hardware Abstraction         4.3.3       Evaluation of Measurement Techniques         4.4       QNX Neutrino on i.MX6Q         4.4       QNX Neutrino on i.MX6Q         4.4       Development Environment         4.4.2       Bord Support Package Configuration         4.4.3       Performance Monitoring Unit         4.4.4       Timer         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.4.6       CRPD Simulation         4.5.1       Development Platform         4.5.2       Timer         4.5.3       MyBarrier         4.5.4       Task Configuration         4.5.5       CRPD Simulation         4.5.6       CRPD Simulation         4.5.7       Timer         4.5.8       S.1         SafeRTOS on i.MX28       S.1.1         Satistics       S.1.2         S.1.1       Statistics         S.1.2       Precision         S.1.3       Figures         S.1.4       Discussion         S.2.1       S                                                                  |          |                                                                                                            |

| 4.2.7       Message Passing         4.3       Abstractions         4.3.1       RTOS Abstraction         4.3.2       Hardware Abstraction         4.3.3       Evaluation of Measurement Techniques         4.4       QNX Neutrino on i.MX6Q         4.4       Development Environment         4.4.2       Bord Support Package Configuration         4.4.3       Performance Monitoring Unit         4.4.4       Timer         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.5.1       Development Platform         4.5.2       Timer         4.5.3       MyBarrier         4.5.4       Task Configuration         4.5.5       CRPD Simulation         4.5.6       CRPD Simulation         4.5.7       Timer         4.5.8       Sold Configuration         4.5.9       Configuration         4.5.1       Statistics         5.1.1       Statistics         5.1.2       Precision         5.1.3       Figures         5.1.4       Discussion         5.2                                                                   |          |                                                                                                            |

| 4.2.7       Message Passing         4.3       Abstractions         4.3.1       RTOS Abstraction         4.3.2       Hardware Abstraction         4.3.3       Evaluation of Measurement Techniques         4.4       QNX Neutrino on i.MX6Q         4.4       Development Environment         4.4.2       Bord Support Package Configuration         4.4.3       Performance Monitoring Unit         4.4.4       Timer         4.4.5       Task Configuration         4.4.5       Task Configuration         4.4.5       Task Configuration         4.4.5       Task Configuration         4.5.5       Task Configuration         4.5.6       CRPD Simulation         4.5.1       Development Platform         4.5.2       Timer         4.5.3       MyBarrier         4.5.4       Task Configuration         4.5.5       CRPD Simulation         5.1       SafeRTOS on i.MX28         5.1.1       Statistics         5.1.2       Precision         5.1.3       Figures         5.1.4       Discussion         5.2       QNX Neutrino in Singlecore mode on i.MX6Q                                                                   |          |                                                                                                            |

| 4.2.7       Message Passing         4.3       Abstractions         4.3.1       RTOS Abstraction         4.3.2       Hardware Abstraction         4.3.3       Evaluation of Measurement Techniques         4.4       QNX Neutrino on i.MX6Q         4.4.1       Development Environment         4.4.2       Bord Support Package Configuration         4.4.3       Performance Monitoring Unit         4.4.4       Timer         4.4.5       Task Configuration         4.4.6       CRPD Simulation         4.5       SafeRTOS on i.MX287         4.5.1       Development Platform         4.5.2       Timer         4.5.3       MyBarrier         4.5.4       Task Configuration         4.5.5       CRPD Simulation         4.5.1       Development Platform         4.5.2       Timer         4.5.3       MyBarrier         4.5.4       Task Configuration         4.5.5       CRPD Simulation         5.1       SafeRTOS on i.MX28         5.1.1       Statistics         5.1.2       Precision         5.1.3       Figures                                                                                                      |          | • •                                                                                                        |

| 4.2.7 Message Passing .         4.3 Abstractions .         4.3.1 RTOS Abstraction         4.3.2 Hardware Abstraction         4.3.3 Evaluation of Measurement Techniques         4.4 QNX Neutrino on i.MX6Q         4.4 QNX Neutrino on i.MX6Q         4.4.1 Development Environment         4.4.2 Bord Support Package Configuration         4.4.3 Performance Monitoring Unit         4.4.4 Timer         4.4.5 Task Configuration         4.4.6 CRPD Simulation         4.5 SafeRTOS on i.MX287         4.5.1 Development Platform         4.5.2 Timer         4.5.3 MyBarrier         4.5.4 Task Configuration         4.5.5 CRPD Simulation         4.5.6 Presults         5.1 SafeRTOS on i.MX28         5.1.1 Statistics         5.1.2 Precision                                                                                                                                                                                                                                                                                                                                                                              |          | 5.1.4 Discussion $\ldots$ |

| <ul> <li>4.2.7 Message Passing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 5.1.3 Figures                                                                                              |

| 4.2.7 Message Passing .         4.3 Abstractions .         4.3.1 RTOS Abstraction         4.3.2 Hardware Abstraction         4.3.3 Evaluation of Measurement Techniques         4.4 QNX Neutrino on i.MX6Q         4.4.1 Development Environment         4.4.2 Bord Support Package Configuration         4.4.3 Performance Monitoring Unit         4.4.4 Timer         4.4.5 Task Configuration         4.4.6 CRPD Simulation         4.5 SafeRTOS on i.MX287         4.5.1 Development Platform         4.5.3 MyBarrier         4.5.4 Task Configuration         4.5.5 CRPD Simulation         4.5.6 CRPD Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | 5.1.2 Precision $\ldots$                                                                                   |

| 4.2.7 Message Passing .4.3 Abstractions .4.3.1 RTOS Abstraction4.3.2 Hardware Abstraction4.3.3 Evaluation of Measurement Techniques4.4 QNX Neutrino on i.MX6Q4.4.1 Development Environment .4.4.2 Bord Support Package Configuration4.4.3 Performance Monitoring Unit4.4.4 Timer4.4.5 Task Configuration4.4.6 CRPD Simulation4.5 SafeRTOS on i.MX2874.5.1 Development Platform4.5.2 Timer4.5.3 MyBarrier4.5.4 Task Configuration4.5.5 CRPD Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | 5.1.1 Statistics $\ldots$ |

| 4.2.7Message Passing4.3Abstractions4.3.1RTOS Abstraction4.3.2Hardware Abstraction4.3.3Evaluation of Measurement Techniques4.4QNX Neutrino on i.MX6Q4.4.1Development Environment4.4.2Bord Support Package Configuration4.4.3Performance Monitoring Unit4.4.4Timer4.4.5Task Configuration4.4.6CRPD Simulation4.5SafeRTOS on i.MX2874.5.1Development Platform4.5.2Timer4.5.3MyBarrier4.5.4Task Configuration4.5.5CRPD Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | 5.1 SafeRTOS on i.MX28                                                                                     |

| 4.2.7 Message Passing4.3 Abstractions4.3.1 RTOS Abstraction4.3.2 Hardware Abstraction4.3.3 Evaluation of Measurement Techniques4.4 QNX Neutrino on i.MX6Q4.4.1 Development Environment4.4.2 Bord Support Package Configuration4.4.3 Performance Monitoring Unit4.4.4 Timer4.4.5 Task Configuration4.4.6 CRPD Simulation4.5 SafeRTOS on i.MX2874.5.1 Development Platform4.5.2 Timer4.5.3 MyBarrier4.5.4 Task Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>5</b> | Results                                                                                                    |

| 4.2.7 Message Passing4.3 Abstractions4.3.1 RTOS Abstraction4.3.2 Hardware Abstraction4.3.3 Evaluation of Measurement Techniques4.4 QNX Neutrino on i.MX6Q4.4.1 Development Environment4.4.2 Bord Support Package Configuration4.4.3 Performance Monitoring Unit4.4.4 Timer4.4.5 Task Configuration4.4.6 CRPD Simulation4.5 SafeRTOS on i.MX2874.5.1 Development Platform4.5.2 Timer4.5.3 MyBarrier4.5.4 Task Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 4.5.5 ORPD SIIIWATION                                                                                      |

| <ul> <li>4.2.7 Message Passing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 8                                                                                                          |

| <ul> <li>4.2.7 Message Passing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |                                                                                                            |

| <ul> <li>4.2.7 Message Passing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 8                                                                                                          |

| <ul> <li>4.2.7 Message Passing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |                                                                                                            |

| <ul> <li>4.2.7 Message Passing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 4.4.3 Performance Monitoring Unit                                                                          |

| <ul> <li>4.2.7 Message Passing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 4.4.2 Bord Support Package Configuration                                                                   |

| <ul> <li>4.2.7 Message Passing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 4.4.1 Development Environment                                                                              |

| 4.2.7       Message Passing         4.3       Abstractions         4.3.1       RTOS Abstraction         4.3.2       Hardware Abstraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | *                                                                                                          |

| 4.2.7       Message Passing         4.3       Abstractions         4.3.1       RTOS Abstraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                                                                                                            |

| 4.2.7       Message Passing         4.3       Abstractions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |                                                                                                            |

| 4.2.7 Message Passing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                                                                                                            |

| *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                                                                                                            |

| 4.2.6 Preemption Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | *                                                                                                          |

# List of Figures

| 2.1         | WCET and BCET 18                                                                                  |

|-------------|---------------------------------------------------------------------------------------------------|

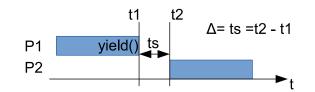

| 2.2         | Context switch time                                                                               |

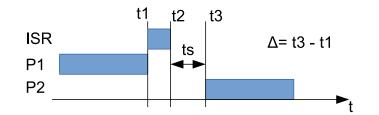

| 2.3         | Preemption time                                                                                   |

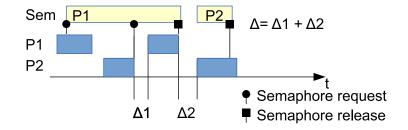

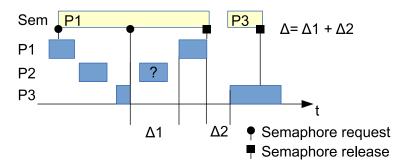

| 2.4         | Semaphore shuffling time 21                                                                       |

| 2.5         | Deadlock breaking time                                                                            |

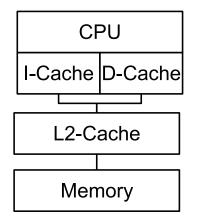

| 2.6         | Singlecore CPU cache                                                                              |

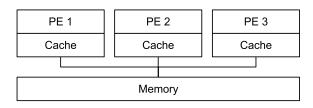

| 2.7         | UMA 27                                                                                            |

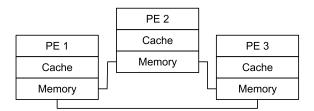

| 2.8         | NUMA                                                                                              |

|             |                                                                                                   |

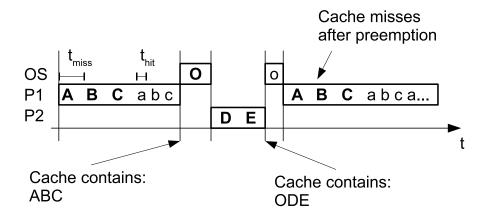

| 3.1         | Cache related preemption delay 38                                                                 |

| 3.2         | Domino effect                                                                                     |

| 3.3         | Multicore context switch time    43                                                               |

| 3.4         | Multicore preemption time    43                                                                   |

| 3.5         | Multicore semaphore shuffle time                                                                  |

| 3.6         | Multicore deadlock break time                                                                     |

| 3.7         | Multicore intertask message passing latency                                                       |

| 3.8         | Profiling suite overview                                                                          |

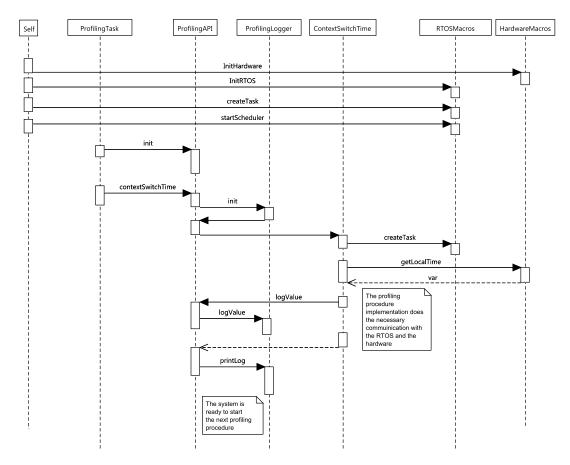

| 3.9         | Sequence diagram of the profiling suite                                                           |

| 4.1         | Overview of the file structure of the profiling suite                                             |

| 4.2         | Evaluation kit for the Freescale i.MX6Q processor                                                 |

| 4.3         | Evaluation kit for the Freescale i.MX28 processor                                                 |

| 1.0         |                                                                                                   |

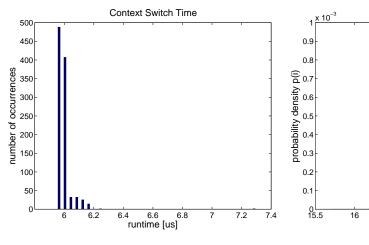

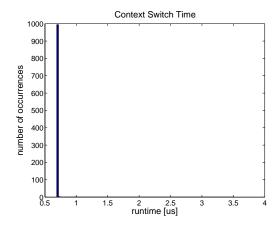

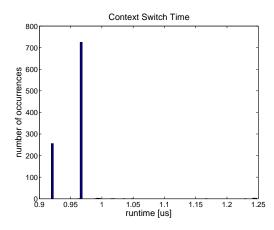

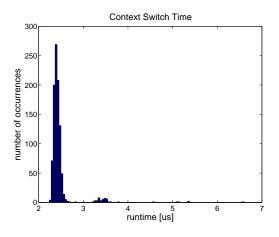

| 5.1         | SafeRTOS without CRPD: Context switch time                                                        |

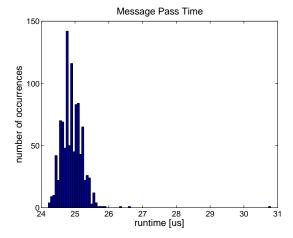

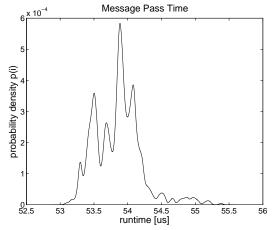

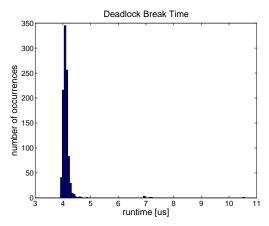

| 5.2         | SafeRTOS without CRPD: Message pass time                                                          |

| 5.3         | SafeRTOS with CRPD: Context switch time                                                           |

| 5.4         | SafeRTOS with CRPD: Message pass time                                                             |

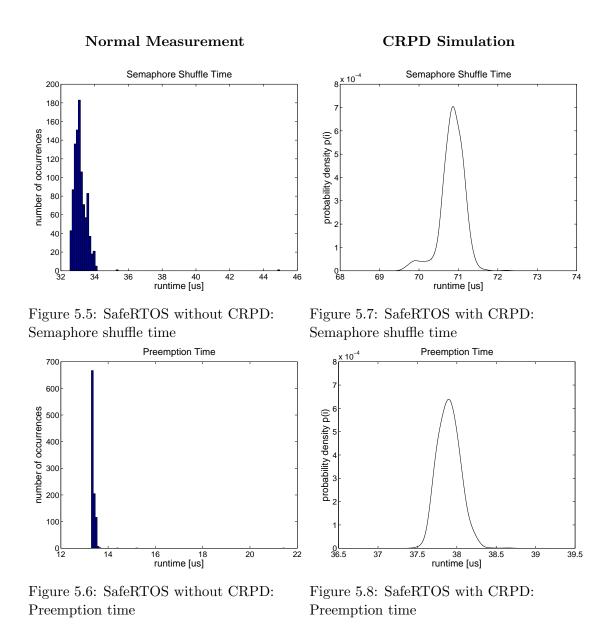

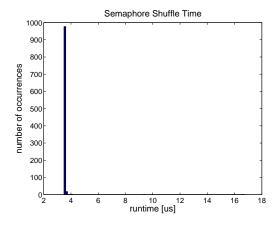

| 5.5         | SafeRTOS without CRPD: Semaphore shuffle time                                                     |

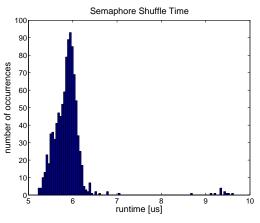

| 5.6         | SafeRTOS without CRPD: Preemption time                                                            |

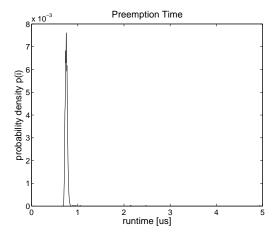

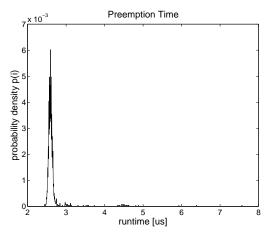

| 5.7         | SafeRTOS with CRPD: Semaphore shuffle time                                                        |

| 5.8         | SafeRTOS with CRPD: Preemption time                                                               |

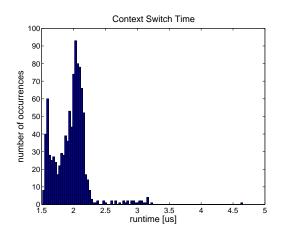

| 5.9         | QNX singlecore without CRPD: Context switch time                                                  |

| 5.10        | QNX singlecore with CRPD: Context switch time                                                     |

| <b>×</b> 11 |                                                                                                   |

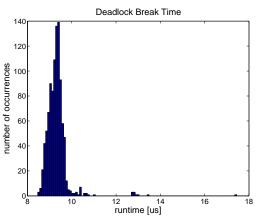

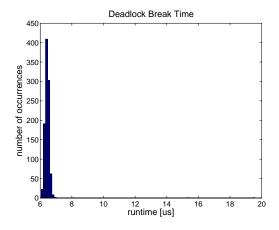

| 5.11        | QNX singlecore without CRPD: Deadlock break time                                                  |

|             | QNX singlecore without CRPD: Deadlock break time78QNX singlecore with CRPD: Deadlock break time78 |

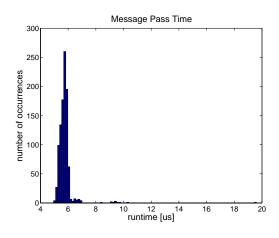

| 5.12        | • •                                                                                               |

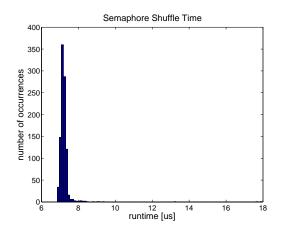

| 5.15 | QNX singlecore without CRPD: Semaphore shuffle time          | 79 |

|------|--------------------------------------------------------------|----|

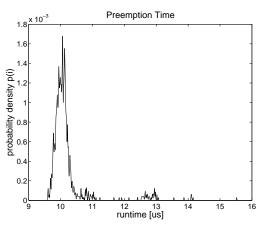

| 5.16 | QNX singlecore with CRPD: Semaphore shuffle time             | 79 |

| 5.17 | QNX singlecore without CRPD: Preemption time                 | 80 |

| 5.18 | QNX singlecore with CRPD: Preemption time                    | 80 |

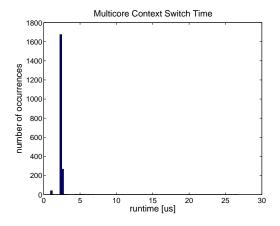

| 5.19 | QNX multicore without CRPD: Context switch time              | 83 |

| 5.20 | QNX multicore with CRPD: Context switch time                 | 83 |

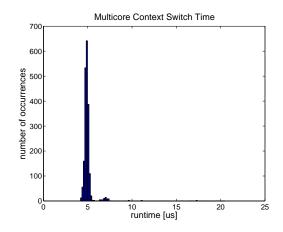

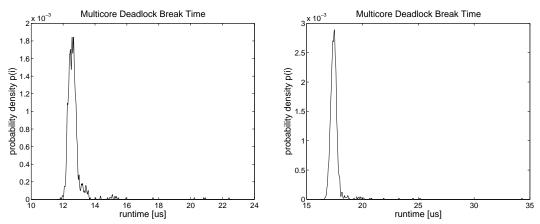

| 5.21 | QNX multicore without CRPD: Deadlock break time              | 84 |

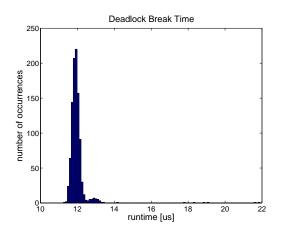

| 5.22 | QNX multicore with CRPD: Deadlock break time                 | 84 |

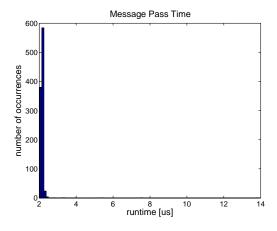

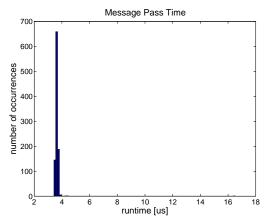

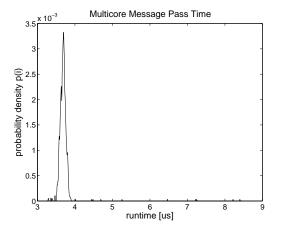

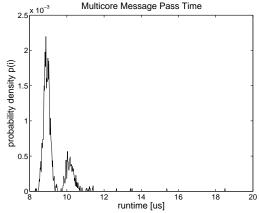

| 5.23 | QNX multicore without CRPD: Message pass time                | 84 |

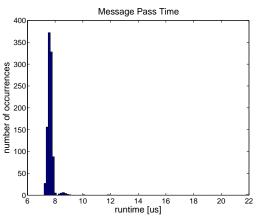

| 5.24 | QNX multicore with CRPD: Message pass time                   | 84 |

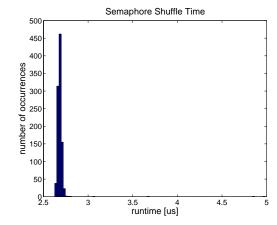

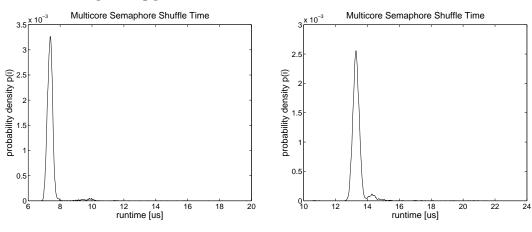

| 5.25 | QNX multicore without CRPD: Semaphore shuffle time           | 85 |

| 5.26 | QNX multicore with CRPD: Semaphore shuffle time              | 85 |

|      | QNX multicore without CRPD: Preemption time                  | 85 |

| 5.28 | QNX multicore with CRPD: Preemption time                     | 85 |

| 5.29 | QNX multicore without CRPD: Multicore context switch time    | 86 |

| 5.30 | QNX multicore with CRPD: Multicore context switch time       | 86 |

| 5.31 | QNX multicore without CRPD: Multicore deadlock break time    | 86 |

| 5.32 | QNX multicore with CRPD: Multicore deadlock break time       | 86 |

| 5.33 | QNX multicore without CRPD: Multicore message pass time      | 87 |

| 5.34 | QNX multicore with CRPD: Multicore message pass time         | 87 |

| 5.35 | QNX multicore without CRPD: Multicore semaphore shuffle time | 87 |

| 5.36 | QNX multicore with CRPD: Multicore semaphore shuffle time    | 87 |

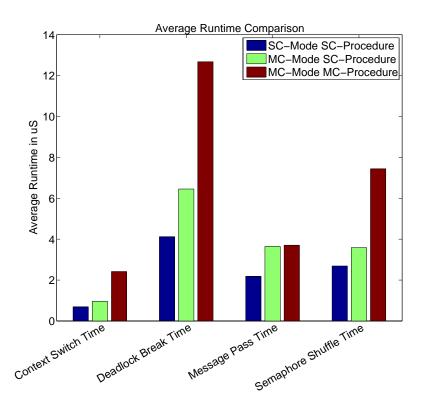

| 5.37 | Average runtimes in single and multicore mode                | 89 |

# List of Tables

| 2.1  | Available RTOS and supported operating modes           | 30 |

|------|--------------------------------------------------------|----|

| 2.2  | RTOS metrics considered important by related works     | 34 |

| 5.1  | SafeRTOS without CRPD simulation                       | 72 |

| 5.2  | SafeRTOS with CRPD simulation                          | 72 |

| 5.3  | SafeRTOS deviations without CRPD simulation            | 72 |

| 5.4  | SafeRTOS deviations with CRPD simulation               | 73 |

| 5.5  | QNX Neutrino without CRPD simulation                   | 76 |

| 5.6  | QNX Neutrino with CRPD simulation                      | 76 |

| 5.7  | QNX singlecore mode deviations without CRPD simulation | 77 |

| 5.8  | QNX singlecore mode deviations with CRPD simulation    | 77 |

| 5.9  | QNX Neutrino BMP without CRPD simulation               | 81 |

| 5.10 | QNX Neutrino BMP with CRPD simulation                  | 82 |

| 5.11 | QNX BMP mode deviations without CRPD simulation        | 82 |

| 5.12 | QNX BMP mode deviations with CRPD simulation           | 83 |

| 5.13 | Overview of average runtimes and standard deviations   | 90 |

|      |                                                        |    |

# Chapter 1

# Introduction

#### 1.1 Motivation

In an industrial and safety-critical real-time system hardware and software has to match safety standards. In order to satisfy all constraints and requirements of a safety standard like the standard of International Electrotechnical Commission (IEC) 61508 an engineer has to pay careful attention to the choice of the components of such a system.

When designing a safety critical real-time system, the first important decision is the processor which needs to satisfy the requirements of the project. In some industrial applications it is required to provide a short reaction time to an event e.g. an analog value. In order to be more flexible and less expensive compared to a solution in hardware, the control system is often designed in pure software and runs as a task on a general purpose CPU. There is a trend to use a multicore processor for such a control system, in order to achieve high calculation speed, short reaction times and flexibility.

The second and also important decision is which safety-certified real-time operating system (RTOS) should be chosen. Such an RTOS provides helpful services, but these services cause overhead, the so called *RTOS Overhead*. This overhead is a necessary parameter to be known when evaluating which RTOS is suitable for an application or how much influence has to be expected by the RTOS services used in the application. A common way to get this information is to measure the runtime of the used RTOS services, which is called RTOS profiling. Most RTOS vendors provide benchmarks for frequently used RTOS services. However, those benchmarks are often performed on a single platform with a defined hardware and operating system configuration. This means that in most cases it is not possible to draw a conclusion from those benchmarked values for a project-specific setup. Also, as said in [Oer12] there is no independent and portable benchmarking or profiling suite for RTOS services. RTOS benchmarking means direct comparison between two or more RTOS. Profiling is more general, it does principally the same as benchmarking, but without enforcing a comparison. Comparing RTOS is possible on small scale processors, but hard and error prone on advanced or even multicore processors. This is, due to the high configurability of these processors and also the RTOS. However, developers of real-time systems still need to know the runtimes of RTOS services on their actual hardware and exactly their configuration of that hardware. Most profiling tools, as for example [JJN08] or [THW10], focus only on application profiling. An RTOS profiling suite would help developers to learn more about exactly their hardware and RTOS environment.

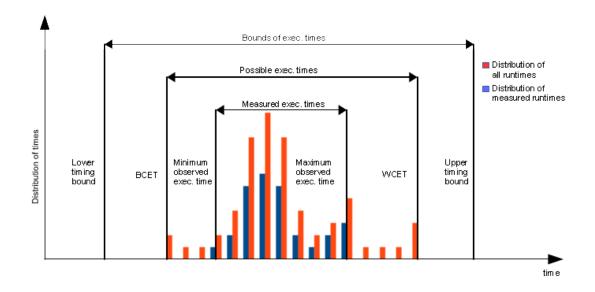

A profiling suite for RTOS is not only useful when deciding which RTOS should be used, because in a safety-critical development process the Worst Case Execution Time (WCET) bounds of a task has to be known in order to do a schedulability analysis. RTOS profiling procedures can also be seen as a special kind of dynamic timing analysis tool designed for operating system services. A dynamic timing analysis is in general not able to find WCET bounds. This is because measuring the start to end time of a function delivers the maximum observed execution time, which is less than the exact WCET [Wil+08].

However, the authors of [Wil+08] further said that safe bounds for the WCET can be found using static timing analysis. In order to do a static timing analysis it is necessary to have an abstract model of the used processor. With this mathematical, abstract and reduced model of the processor the binary file of the application is analyzed in order to find the worst case path of a function or method. The user of such a static analysis tool needs to provide some annotations like maximal expected loop iteration or maximum queue depth [Wil+08].

A static timing analysis achieves the safety by the additional effort of defining a model of the processor and calculating the worst case execution paths through the program using the users annotations and configurations. It is recommended to evaluate the results of the static timing analysis by measuring the runtime on the target system, because annotations taken by the user or the configuration of the processor may be wrong. It is clear that a lower calculated WCET than the measured execution time indicates a wrong annotation for the static timing analysis, but also a much higher value of the calculated WCET indicates a problem with the static timing analysis [Wil+08].

A profiling suite for RTOS would make it easier to assist static WCET analysis generating tight bounds for runtimes, because the profiling procedures can be used to check the annotations. As said in [Oer12] there is a lack of vendor-neutral benchmarking suits for RTOS. This is problematic, because vendors might have optimized their RTOS for their benchmarking procedures. Hence, our profiling suite is created without any RTOS vendor support.

Furthermore, there is also a trend for safety-certified RTOS to implement the support for multicore processors. Actually there is also a lack of profiling procedures for RTOS services that can handle multicore systems. That means that it would be helpful to have a vendor neutral profiling suite that also supports multicore processors when designing a safety critical real-time system and later to evaluate the performance of a static WCET analysis for system services.

This leads to the following questions:

- What is required to design a profiling suite that is portable to multiple RTOSs and compatible with single- and multi-processor systems?

- What are meaningful metrics of an RTOS that supports only singlecore processors?

- What are meaningful metrics of an RTOS that supports multicore processors?

- Which existing profiling methods RTOS services can be extended to be compatible with multicore processors?

- How can profiling methods be implemented, such that they are portable between different platforms?

### 1.2 Goals

The overall goal of this work is the implementation of a profiling suite for safet-certified RTOS which supports the following: vendor neutrality, meaningful profiling procedures, support for multicore compatible RTOS and simplicity of use and platform porting.

To reach this overall goal five subgoals are defined:

- 1. An evaluation of state-of-the-art RTOS benchmarking methods. The evaluation results deliver a list of possible profiling procedures for our profiling suite.

- 2. An evaluation of a defined selection of multicore architectures in combination with an also defined number of RTOSs. This evaluation results in a strategy for extending the profiling procedures in the first point to be suitable for multicore compatible RTOSs.

- 3. With the knowledge which profiling procedures will be implemented for our profiling suite, a user-friendly adaptation-layer is defined. This adaptation-layer is used to provide an interface for the profiling procedures. The user of the benchmarking suite will adapt the adaptation-layer to fit the specific hardware platform and RTOS.

- 4. Porting the profiling suite to the in point two selected hardware and RTOS. This results in a evaluation of these hardware and software platforms.

### 1.3 Outline

In Chapter 2 the necessary technical background to understand the further chapters is presented. After that a survey of related works is done and a comparison of important RTOS metrics is shown.

Chapter 3 introduces the concept and design of the profiling suite. The concept focuses on the coverage of important details of advanced processor architectures and how to deal with them. The design is made in a way such that porting between RTOS and hardware and implementation of additional profiling procedures is simple.

The implementation of the profiling suite is described in Chapter 4. Furthermore, problems and implementation details on every hardware and RTOS are stated.

The measurement results can be found in Chapter 5. The results cover singlecore measurements on SafeRTOS and QNX Neutrino and multicore measurements on QNX Neutrino in BMP mode.

The last two Chapters 6 and 7 conclude the work and recommend possible ways to further improve the profiling suite.

# Chapter 2

# Technical Background and Related Work

This chapter covers the basic background knowledge of real-time operating systems and timing analysis. Furthermore, the architecture of real-time systems is described with a focus on multiprocessor system-on-chip and the differences regarding profiling are stated. Thereafter the current existing approaches are described in the related work section.

### 2.1 Real-time Systems

A real-time system guaranties a reaction to an event within a given timeslot. The end of the timeslot is called a deadline. Real-time systems also provide deterministic and consistent behavior, which is necessary in order to verify the systems timing behavior. Real-time systems can be classified by the consequence of missing a deadline [LY03]:

Hard Real-Time System: Missing a deadline could have serious consequences.

**Soft Real-Time System:** A late value is not useless at all, but a missed deadline often means that the quality-of-service decreases.

In this work we focus on hard real-time systems, which can be found for example in an aircraft, a power station or a car. Missing a deadline in such a safety-critical system can endanger human life. In order to ensure that the system reacts within the specified time limits on the event, it is important to know how long it takes to deliver the result in the worst case. How worst case times can be found will be explained later in this chapter.

## 2.2 Real-time Operating Systems

Real-time Operating Systems (RTOS) are intended to make it easier to develop a realtime system. The RTOS provides features such as scheduling, interprocess communication, semaphores and resource management [LY03]. An RTOS reduces not just the development time of an embedded system, especially in a safety-critical system it is highly recommended to utilize a certified RTOS. It is beneficial, because it minimizes the probability of making a mistake when implementing RTOS services.

#### 2.2.1 Processes and Tasks

One of the central responsibility of an RTOS is to manage more than one task at a time [Tan07]. Therefore the operating system schedules tasks sorted by their priorities. A task can either be a process or a thread.

- **Process:** A process is the most heavyweight construct. Processes are scheduled by the RTOS and have their own address spaces [Tan07]. If there exists more than one process in the system, the processes need a control block and may have a priority. It is also necessary that the processor provides a memory management unit (MMU) in order to switch between the address spaces. Low-end microcontroller often lack of such an MMU. Thus small scale RTOS often have only a single process, which uses threads that share the same address space.

- **Thread:** A thread is owned by a process and is also scheduled by the RTOS. Threads have their own control blocks including the priorities and the stacks [Tan07].

- **Coroutine:** Coroutines belong to a process or thread and share their address spaces, stacks and heaps. Coroutines are scheduled by the process or thread they belong to. The scheduling is done cooperative.

Depending on the scheduling policy, processes and threads may be preemtable either at a special scheduling point in the code or at any time when an event occurs [Tan07].

#### 2.2.2 Scheduling

The scheduler of an RTOS decides which task should be started next and which will be suspended. The aim of a scheduler in a real-time system is to comply with deadlines and to be predictable. Tasks might occur either periodic or aperiodic. Aperiodic means that the task may occur unpredictable.

In general a set of tasks is said schedulable, if the following condition holds:

$$\sum_{i=1}^{m} \frac{C_i}{P_i} \le 1 \tag{2.1}$$

Where  $C_i$  is the execution time of the task *i*,  $P_i$  is the period of task *i* and *m* the number of tasks in the set [Tan07].

A set of tasks may be scheduled static, which means that the schedule is defined at compile time. However, exact information about the deadlines and the work has to be available beforehand. In contrast to static scheduling, dynamic scheduling decides at runtime which task should be scheduled next [Tan07].

Dynamic scheduling can be either preemptive or non-preemptive. That means, a preemptive scheduler can interrupt a running task at any time, but a non-preemptive scheduler has to wait until the running process ends or suspends voluntarily. An example for non-preemptive scheduling is cooperative scheduling. Preemptive algorithms are priority first-in-first-out (FIFO) with time slicing, round robin, rate monotonic scheduling and earliest deadline first [LY03] [Tan07]. In [TTN09] the authors present a comparison of RTOSs including their scheduling strategies. Most compared RTOSs use priority FIFO with time slicing due to the low overhead and good predictability.

#### 2.2.3 Interprocess Communication

According to [Tan07] interprocess communication (IPC) contains three subtasks.

- 1. Communication between processes the so-called message passing.

- 2. Protection of shared resources and critical regions, the mutual exclusion.

- 3. The barrier, where a process A produces data, which will be used by another process B. B has to wait until A has completed the production.

For further information on IPC we refer the reader to [Tan07] Chapter 2.

#### 2.2.4 Interrupts

One of the most important tasks of an RTOS is to react on an interrupt event. Such an event is handled by an Interrupt Service Routine (ISR). If an interrupt occurs the processor saves the state and jumps to the ISR [LY03].

It is a design decision of the embedded system designer where to do the full handling of an interrupt. It could either be done directly in the ISR or the ISR is only used to notify a task about the occurrence of the interrupt. The first method is faster because no scheduling is necessary, but the drawback is that while the ISR is executed, other interrupts may be blocked.

#### 2.2.5 **Priority Inversion**

Assume, there are three tasks with different priorities, A, B and C, running on a RTOS. The lowest priority task A acquires a lock. After that the highest priority task C tries to acquire the same lock, which means that C has to wait until A releases the lock. However, that will not happen until task B stops the execution and A can finish its work. Due to this fact, C will probably miss its deadline. To avoid such a situation some RTOSs contain a priority inheritance protocol, in which the task that holds the lock, inherits the priority of the highest priority process that tries to acquire the same lock [LY03]. Using such a protocol task A in our example would get the priority of task C, so it would be scheduled before B.

#### 2.2.6 Application Programming Interface